Future Corporation Develops Proprietary FPGA-Based AI Accelerator

Future Corporation, a social design company with over 20 group companies, has announced the development of a proprietary AI accelerator, codenamed “Mark-I.” This accelerator, designed to enhance the speed of AI processing, was developed by ki-labs (Key-I Labs), a research and development organization established in October 2024 with the aim of advancing future computing technology and business. The “Mark-I” will be unveiled for the first time at “RISC-V Day Tokyo 2026 Spring,” held on March 5, 2026, at the Ito International Research Center, The University of Tokyo.

Future Corporation has been actively promoting academic research and development in AI through its Strategic AI Group. In October 2024, the company was selected for the “GENIAC (Generative AI Accelerator Challenge)” project, promoted by the Ministry of Economy, Trade and Industry (METI) and the New Energy and Industrial Technology Development Organization (NEDO). Through this project, Future Corporation successfully built a foundational model specialized in Japanese and software development in collaboration with various university research laboratories. Details on this achievement were released on June 9, 2025:

Under the slogan “Designing Management and AI,” Future Corporation, together with its core operating company Future Architect, provides AI consulting services to address clients’ management and societal challenges. As AI adoption accelerates, the limitations of software optimization in terms of processing performance and power efficiency become apparent. The AI accelerator developed by ki-labs aims to resolve these challenges from a hardware perspective.

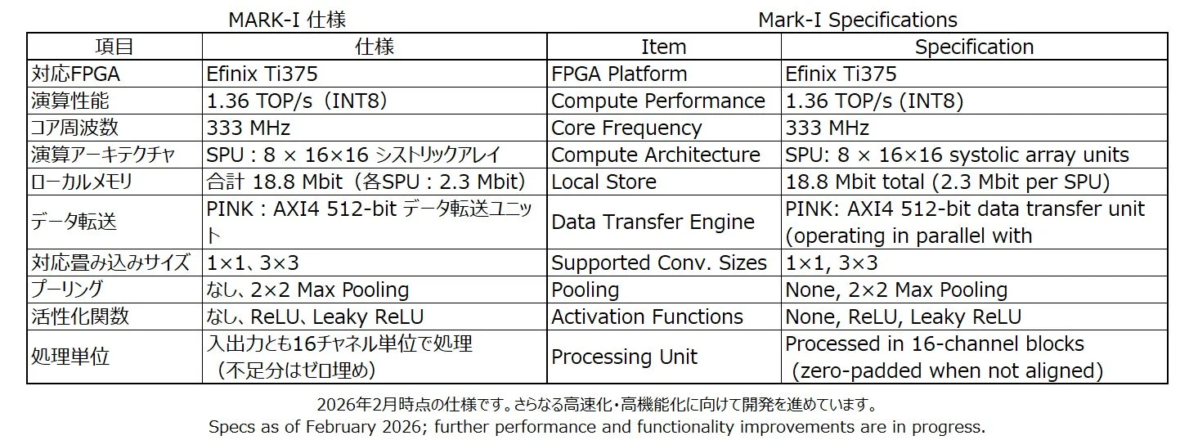

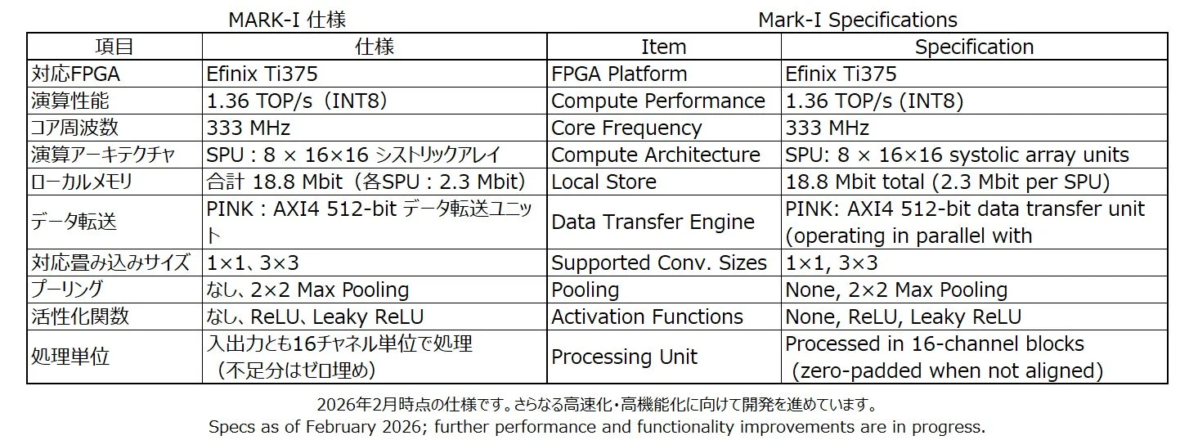

Features of the “Mark-I” AI Accelerator

The “Mark-I” AI accelerator incorporates eight systolic arrays, enabling high-speed processing of Convolutional Neural Networks (CNNs). By adopting Field Programmable Gate Array (FPGA) technology, the accelerator allows for flexible configuration changes (full customization) according to specific applications. This provides a significant advantage in real-time processing at the edge, such as facial detection. A key feature of “Mark-I” is that all aspects, from circuit design source code (SystemVerilog) to control software, are developed in-house. It employs the RISC-V architecture for its controller, and software developed in Rust ensures efficient and precise data flow control. This enables full customization and optimization tailored to the specific AI application.

Future Corporation is integrating its extensive knowledge gained from large-scale mission-critical and accounting system development projects with advanced AI technology. By combining its proprietary AI accelerator with the customizable AI hardware “Mark-I,” the company aims to establish a new digital foundation that fosters future business innovation. Future Corporation will continue to support corporate digital transformation (DX) by providing end-to-end services, from formulating management strategies to designing AI models and implementing AI hardware.

“RISC-V Day Tokyo 2026 Spring” Exhibition Details

The “Mark-I” will be showcased at “RISC-V Day Tokyo 2026 Spring,” the largest technical conference in Japan focusing on the open-source instruction set architecture, RISC-V. The event has been held annually since 2017, bringing together leading domestic and international companies, students, and researchers to share insights on the latest trends in chip design, AI accelerators, and security technologies.

-

Date and Time: March 5, 2026 (Thursday), 9:00 – 18:00

-

Venue: Ito International Research Center, The University of Tokyo (7-3-1 Hongo, Bunkyo-ku, Tokyo)

-

Organizer: RISC-V Association

-

Admission Fee: Free (pre-registration required)

-

Official Website: https://riscv.or.jp/risc-v-day-tokyo-2026-spring-j/

During the exhibition, a demonstration of real-time object detection using “Mark-I” will be conducted. The demonstration will show how the edge FPGA can detect human faces in real time and convert them into metadata, illustrating an approach to AI utilization that prioritizes privacy. Additionally, a 20-minute presentation titled “Case Study of Custom AI Accelerator Development Utilizing RISC-V” will be delivered starting at 16:30.

Customer Inquiries Regarding This Project

Future Corporation ki-labs (Key-I Labs): Miyashita, Kitamoto